AJADONISI

digital

# peripherals handbook

programming • interfacing

digital

## peripherals handbook

programming • interfacing

digital equipment corporation

Copyright © 1973, by Digital Equipment Corporation

DEC, PDP, UNIBUS are registered trademarks of Digital Equipment Corporation.

## **TABLE OF CONTENTS**

| CHAPTER 1 INTRODUCTION                    |      |

|-------------------------------------------|------|

| 1.1 GENERAL                               | 1-1  |

| 1.2 SCOPE AND CONTENTS                    | 1-1  |

| 1.3 REFERENCES                            | 1-2  |

| 1.4 PERIPHERALS                           | 1-2  |

| 1.5 UNIBUS                                | 1-2  |

| 1.6 CENTRAL PROCESSOR                     | 1.3  |

|                                           | 1.3  |

| 1.7 SOFTWARE                              |      |

| 1.8 PDP-11 WORD                           | 1-4  |

| CHAPTER 2 PROGRAMMING                     |      |

|                                           |      |

| 2.1 GENERAL                               | 2-1  |

| 2.2 ADDRESSES                             | 2-1  |

| 2.3 DEVICE REGISTERS                      | 2-2  |

| 2.4 PROCESSOR REGISTERS                   | 2-3  |

| 2.4.1 General Registers                   | 2-3  |

| 2.4.2 Processor Status Word               | 2-4  |

| 2.5 INTERRUPT STRUCTURE                   | 2-5  |

| 2.6 PROGRAMMING WITH DEVICE REGISTERS     |      |

| 2.7 DEVICE PRIORITY                       |      |

|                                           | -2-7 |

| CHAPTER 3 CATEGORIES OF PERIPHERALS       |      |

| 3.1 GENERAL                               | 3-1  |

|                                           | 3-1  |

| 3.2 MAIN MEMORY                           | 3-1  |

| 3.3 TERMINALS                             |      |

| 3.4 PAPER TAPE                            | 3-3  |

| 3.5 CARDS                                 | 3-3  |

| 3.6 PRINTERS                              | 3-3  |

| 3.7 MAGNETIC TAPE                         | 3-4  |

| 3.8 DISKS                                 | 3-4  |

| 3.9 DISPLAYS                              | 3-4  |

| 3.10 COMMUNICATIONS                       | 3-5  |

| 3.11 DATA ACQUISITION                     | 3-6  |

| 3.12 UNIBUS EQUIPMENT                     | 3-7  |

| 3.13 MOUNTING EQUIPMENT                   | 3-7  |

|                                           | •    |

| CHAPTER 4 DESCRIPTIONS OF PERIPHERALS     |      |

| 4.1 INTRODUCTION                          | 4-1  |

| 4.2 EXPLANATION OF TERMS & SPECIFICATIONS | 4-1  |

| 4.2.1 Products                            | 4-1  |

| 4.2.2 Registers                           | 4-1  |

|                                           | 4-2  |

| 4.2.3 Specifications                      |      |

| 4.2.4 Conversion Factors                  | 4-3  |

| 4.3 LIST OF PERIPHERALS                   | 4-3  |

| CHAPTER 5 UNIBUS THEORY AND OPERATION     |      |

|                                           |      |

| 5.1 INTRODUCTION                          |      |

| 5.1.1 Single Bus                          | 5-1  |

| 5.1.2 Bidirectional Lines                 | 5-1  |

|             | 5.1.3 Master-Slave Relation 5.1.4 Interlocked Communication | 5-1<br>5-2 |

|-------------|-------------------------------------------------------------|------------|

|             | PERIPHERAL DEVICE ORGANIZATION AND CONTROL                  | 5-2        |

| 5.3         | TRANSFER OF BUS MASTER                                      | 5-2        |

|             | 5.3.1 Transfer Request Handling                             | 5-2        |

|             | 5.3.2 Priority Structure                                    |            |

|             | 5.3.3 Data Transfer                                         | 5-3        |

|             | 5.3.4 Interrupt Requests                                    | 5-3        |

|             | 5.3.5 Interrupt Procedure                                   | 5-3        |

|             | UNIBUS SIGNAL LINES                                         | 5-4        |

|             | DATA TRANSFERS                                              | 5-6        |

|             | 5.5.1 Signals used in Data Transfer                         | 5-6        |

|             | 5.5.2 Direction of Data Transfer                            | 5-7        |

|             | 5.5.3 Conventions and Definitions                           | 5-9        |

| -           | 5.5.4 Equivalent Logic at the Slave                         | 5-10       |

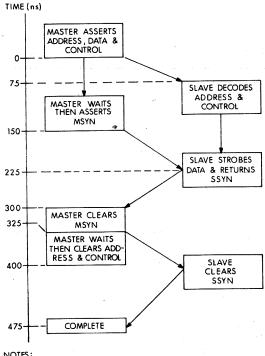

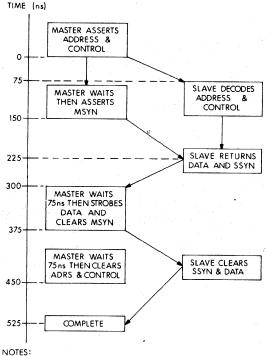

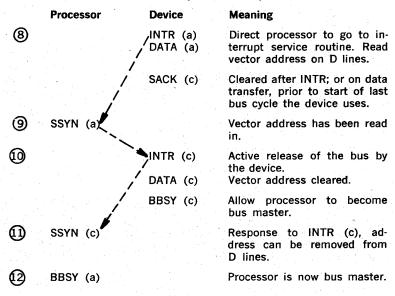

|             | 5.5.5 Data Transfer Timing                                  | 5-11       |

|             | 5.5.6 DATI and DATIP Bus Transactions                       | 5-12       |

|             | 5.5.7 DATO and DATOB Bus Transactions                       | 5-14       |

|             | 5.5.8 Timing Examples                                       | 5-16       |

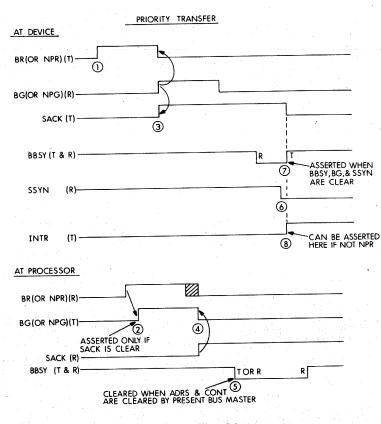

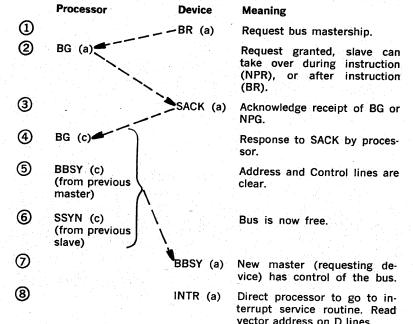

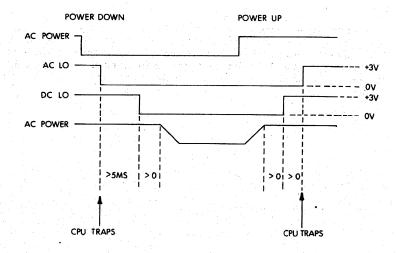

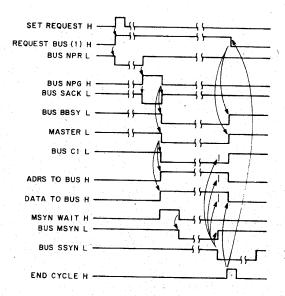

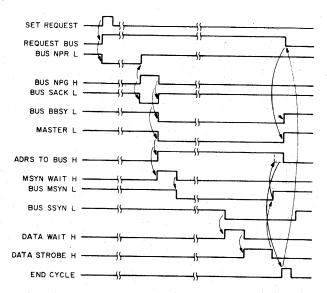

| 5.6         | PRIORITY TRANSFERS                                          | 5-17       |

|             | 5.6.1 Signals used in Priority Transfer                     | 5-17       |

|             | 5.6.2 Transfer of Control                                   | 5-19       |

|             | 5.6.3 Priority Transfer                                     | 5-19       |

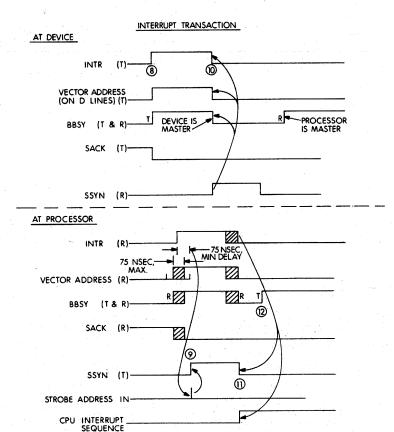

|             | 5.6.4 Interrupt Operation                                   | 5-22       |

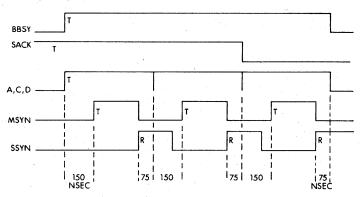

| 5.7         | MISCELLANEOUS CONTROL LINES                                 | 5-24       |

|             | SUMMARY OF UNIBUS SIGNALS                                   | 5-26       |

| 5.9         | UNIBUS                                                      | 5-28       |

|             | 5.9.1 Timing                                                | 5-28       |

|             | 5.9.2 Time-Out Protection                                   | 5-28       |

|             | 5.9.3 Priority Chaining                                     | 5-28       |

|             | 5.9.4 Address Mapping                                       | 5-29       |

| <b>5</b> 10 | 5.9.5 Device Registers                                      | 5-31       |

| 5.10        | COMPARISON BETWEEN NPR & BR OPERATION                       | 5-33       |

| CHAPTE      | R 6 UNIBUS INTERFACING                                      |            |

| 6.1         | GENERAL                                                     | 6-1        |

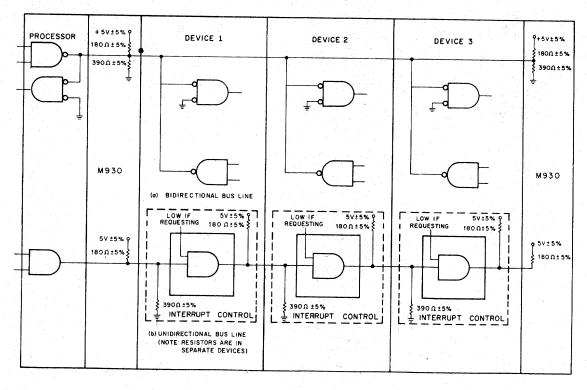

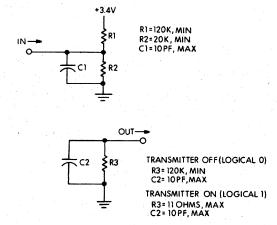

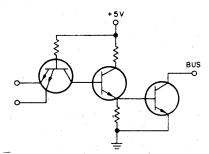

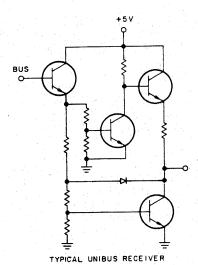

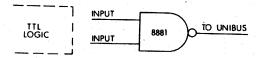

|             | 6.1.1 UNIBUS Transmission                                   | 6-1        |

|             | 6.1.2 UNIBUS Signal Levels                                  | 6-1        |

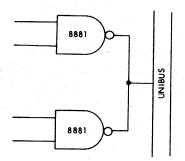

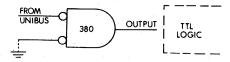

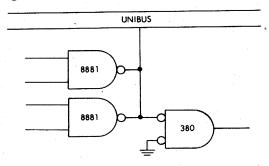

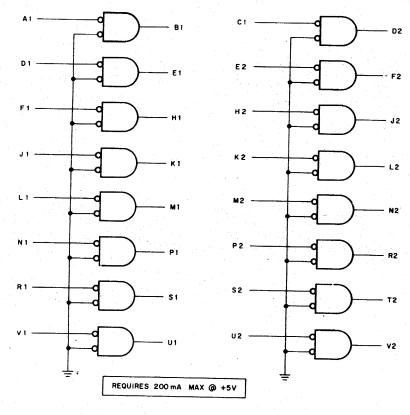

|             | 6.1.3 Bus Receiver and Transmitter Circuits                 | 6-3        |

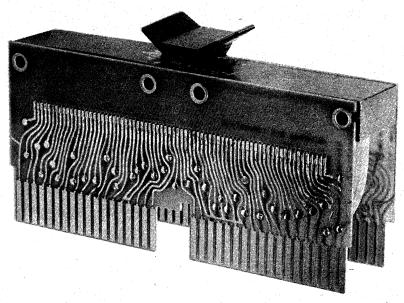

|             | 6.1.4 UNIBUS Length and Loading                             | 6-6        |

| 6.2         | UNIBUS INTERFACE MODULES                                    | 6-7        |

|             | 6.2.1 BC11A, UNIBUS CABLE                                   | 6-8        |

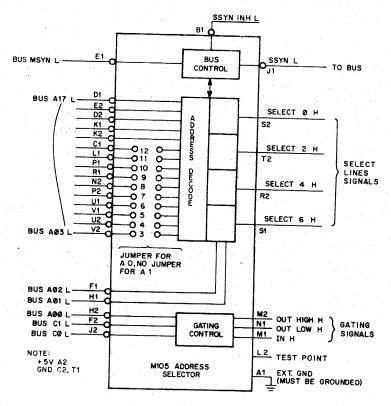

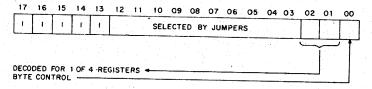

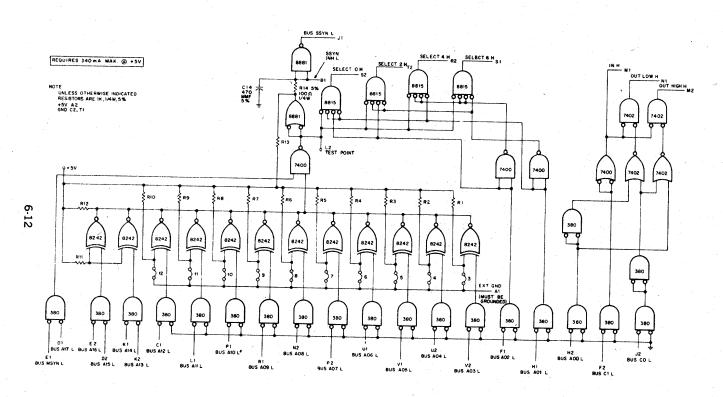

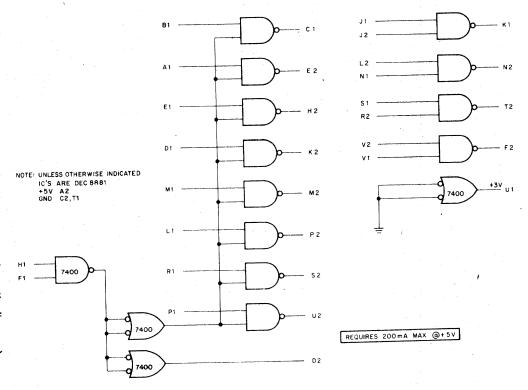

|             | 6.2.2 M105, Address Selector Module                         | 6-9        |

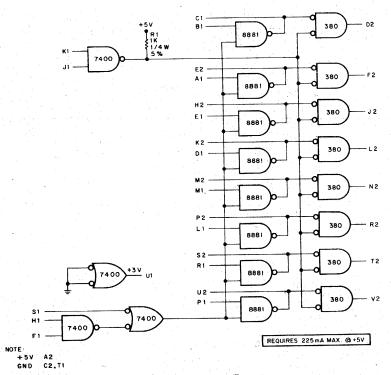

|             | 6.2.3 M783, UNIBUS Transmitter Module                       | 6-11       |

|             | 6.2.4 M784, UNIBUS Receiver Module                          | 6-11       |

|             | 6.2.5 M785, UNIBUS Transceiver Module                       | 6-13       |

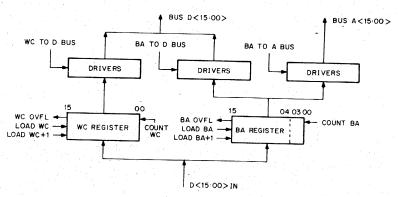

|             | 6.2.6 M795, Word Count and Bus Address Module               | 6-14       |

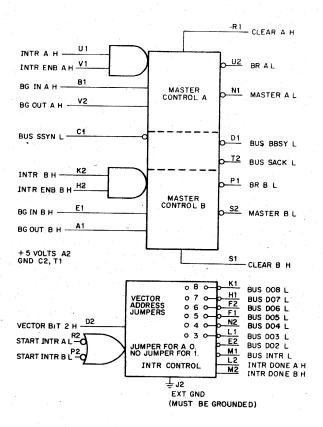

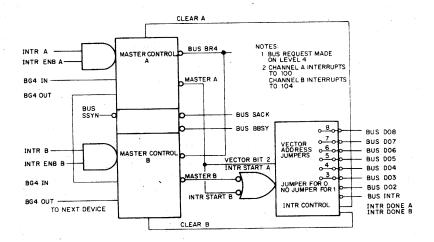

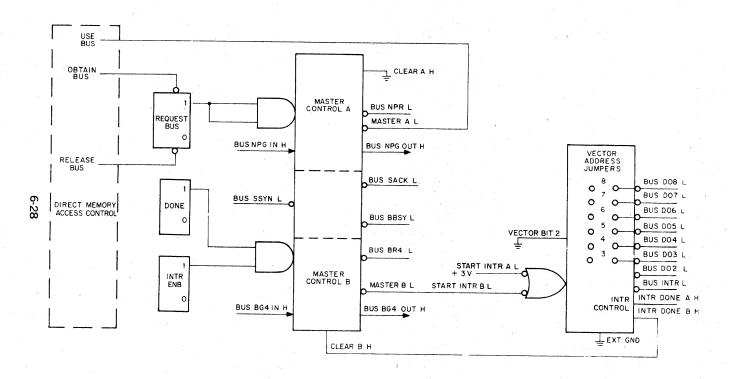

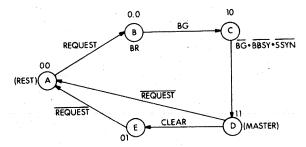

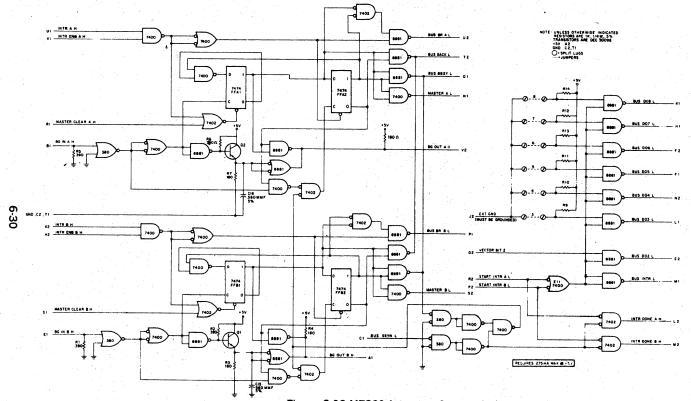

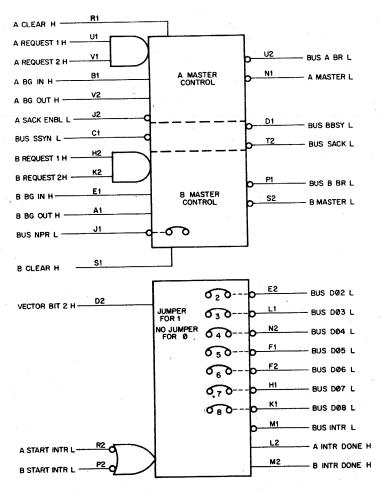

|             | 6.2.7 M796, UNIBUS Master Control Module                    | 6-17       |

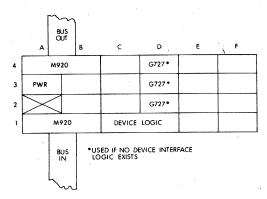

|             | 6.2.8 M920, UNIBUS Jumper Module                            | 6-24       |

|             | 6.2.9 M930, UNIBUS Terminator Module                        | 6-24       |

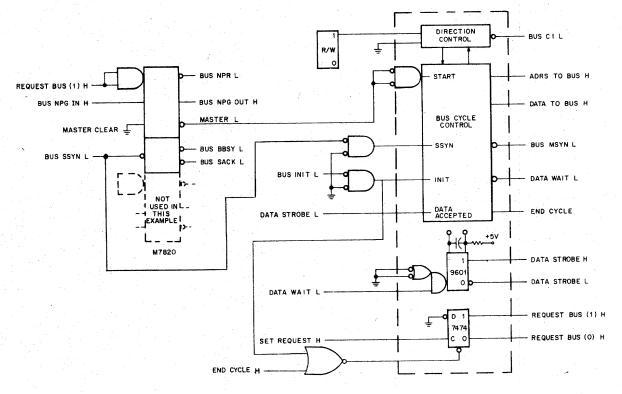

|             | 6.2.10 M7820, Interrupt Control Module                      | 6-25       |

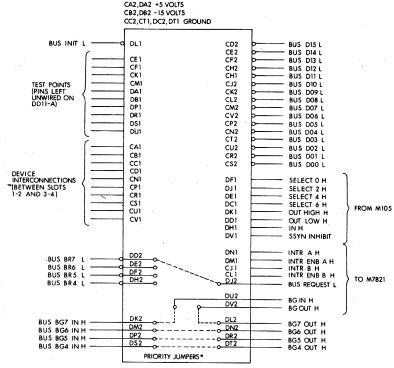

|             | 6.2.11 M7821, Interrupt Control Module                      | 6-29       |

|             |                                                             |            |

| CHAPTER 7 INTERFACE EXAMPLES                            |              |

|---------------------------------------------------------|--------------|

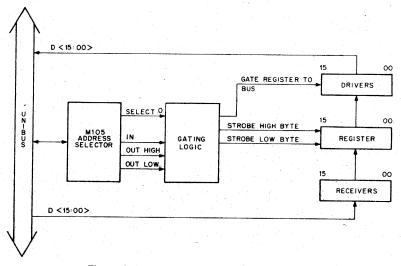

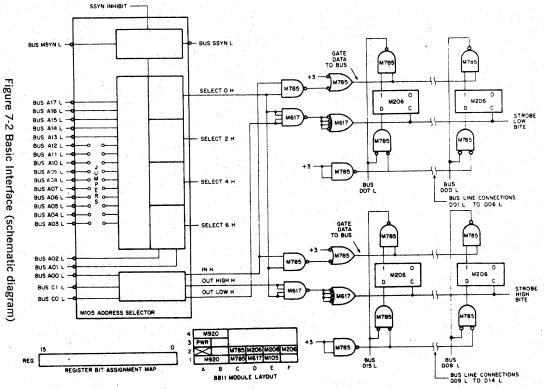

| 7.1 BASIC INTERFACE                                     | 7-1          |

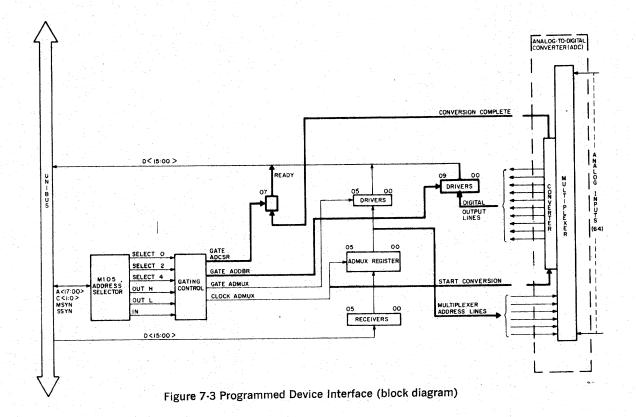

| 7.2 PROGRAMMED DEVICE INTERFACE                         | 7-4          |

| 7.3 INTERRUPT SERVICED INTERFACE                        | 7-8          |

| 7.4 DIRECT MEMORY ACCESS (DMA) INTERFACE                | 7-13         |

| 7.5 OUTPUT INTERFACE WITH INTERRUPT CONTROL             | 7-15         |

| 7.6 DAC-DMA INTERFACE                                   | 7-19         |

|                                                         |              |

| CHAPTER 8 SITE PLANNING                                 | <u> </u>     |

| 8.1 GENERAL                                             | 8-1          |

| 8.1.1 Scope                                             | 8-1          |

| 8.1.2 Planning Assistance                               | 8-1          |

| 8.1.3 Installation Constraints                          | 8-1          |

| 8.2 COMPUTER SITE                                       | 8-1          |

| 8.2.1 Site Considerations                               | 8-1          |

| 8.2.2 System Reliability                                | 8-3          |

| 8.2.3 System Environment                                | 8-4          |

| 8.2.4 Size of Systems                                   | 8-6          |

| 8.3 POWER                                               | 8-8<br>8-8   |

| 8.3.1 Power Origination and Connections                 | 8-8          |

| 8.3.2 Grounding                                         |              |

| 8.3.3 Customer Supplied Power                           | 8-10<br>8-10 |

| 8.4 POWER CONTROL SYSTEM                                | 0.10         |

| CHAPTER 9 CONFIGURATION GUIDE                           |              |

| 9.1 GENERAL                                             | 9-1          |

| 9.1.1 Configuring a System                              | 9-1          |

| 9.1.2 UNIBUS                                            | 9-1          |

| 9.1.3 Latency                                           | 9-1          |

| 9.1.4 References                                        | 9-2          |

| 9.2 MOUNTING EQUIPMENT                                  | 9-2          |

| 9.3 CONFIGURATIONS                                      | 9-5          |

| 9.3.1 Configuration Diagrams                            | 9-5          |

| 9.3.2 Configuration Guidelines                          | 9-5          |

|                                                         |              |

|                                                         |              |

|                                                         |              |

|                                                         |              |

| Appendix A UNIBUS Addresses                             | A-1          |

| Appendix B Miscellaneous Tables and Data                | B-1          |

| B.1 UNIBUS Pin Assignments (by pin numbers)             | B-1          |

| B.2 UNIBUS Pin Assignments (by signal name)             | B-2          |

| B.3 BB11 Power Pin Assignments                          | B-3          |

| B.4 ASCII Code                                          | B-4          |

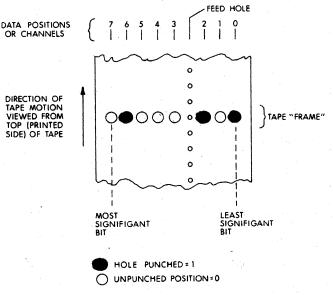

| B.5 Paper Tape Format                                   | B-5          |

| B.6 Punched Card Format                                 | B-6          |

| Appendix C Summary of PDP-11 Instructions               | C-1          |

|                                                         |              |

| Appendix D PDP-11 Assembly Language                     |              |

| Appendix F. Summary of Equipment Specifications & Index | E-1          |

#### CHAPTER 1

## INTRODUCTION

#### 1.1 GENERAL

The PDP-11 family is a comprehensive set of hardware/software facilities that includes several computers, a large number of peripheral devices and options, and extensive software. New systems will be compatible with existing family members. The user can choose the system which is most suitable for his application, but as needs change or grow he can easily add or change equipment.

#### Some of the characteristics of PDP-11 equipment are:

- 16-bit word (two 8-bit bytes) direct addressing of 32K 16-bit words or 64K 8-bit bytes (K = 1024)

- Word or byte processing central processors are hardwired for word and byte instructions

- Asynchronous operation systems run at their highest possible speed, replacement with faster devices means faster operation with no other hardware or software changes

- Modular component design extreme ease and flexibility in configuring systems

- Direct Memory Access (DMA) inherent in the architecture is direct memory access for multiple devices

- Automatic Priority Interrupt four-line, multi-level system permits grouping of interrupt lines according to response requirements

- Vectored interrupts

fast interrupt response without device polling

- Power Fail & Automatic Restart hardware detection and software protection for fluctuations in the AC power

#### 1.2 SCOPE AND CONTENTS

This Handbook is intended to be a reference for PDP-11 equipment, other than central processors. Descriptions, specifications, programming, and interfacing information is presented on the PDP-11 peripherals and options.

#### **Peripherals**

| Programming                       | (chapter 2)  |

|-----------------------------------|--------------|

| General comparisons               | (chapter 3)  |

| Descriptions                      | (chapter 4)  |

| Configuration guide               | (chapter 9)  |

| Summary of specifications & Index | (appendix E) |

| Summary of specifications & index | (appendix E) |

**Programming**

| Applied to peripherals         | (chapter 2)  |

|--------------------------------|--------------|

| Device registers and examples  | (chapter 4)  |

| Summary of PDP-11 instructions | (appendix C) |

| PDP-11 Assembly Language       | (appendix D) |

#### UNIBUS

| Operation   | (chapter 5)  |

|-------------|--------------|

| Circuitry   | (chapter 6)  |

| Interfacing | (chapter 7)  |

| Addresses   | (appendix A) |

| Pin numbers | (appendix B) |

#### Supplementary Information

| Site planning        | (chapter 8)  |

|----------------------|--------------|

| Miscellaneous tables | (appendix B) |

#### 1.3 REFERENCES

The information in the Handbook supplements material found in:

#### PDP-11 Processor Handbook

Processor Handbooks are available for the various PDP-11 computers. Familiarity with or access to such a Handbook would greatly facilitate an understanding of the material in this Handbook. However, some introductory PDP-11 information is included in this Handbook.

#### 1.4 PERIPHERALS

Digital Equipment Corporation designs and manufactures many of the peripheral devices offered with PDP-11's. As a designer and manufacturer of peripherals, Digital can offer extremely reliable equipment, lower prices, more choice and quantity discounts.

#### 1.5 UNIBUS

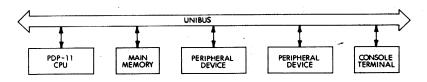

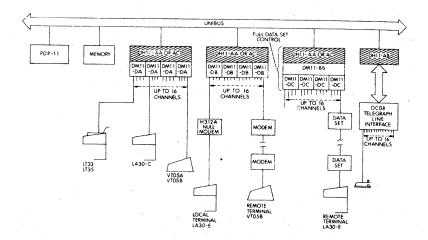

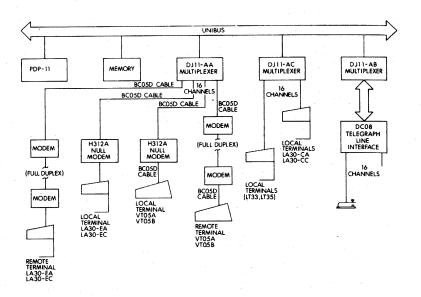

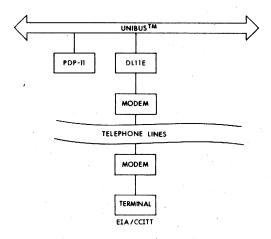

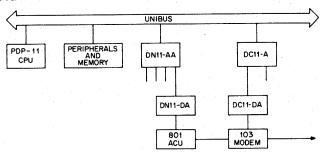

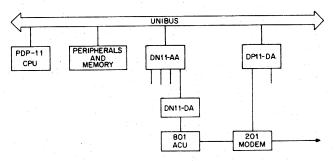

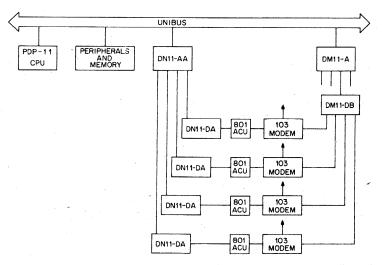

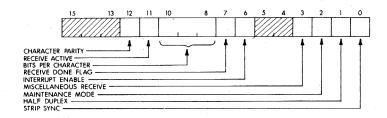

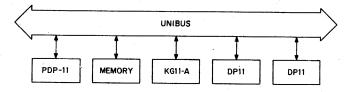

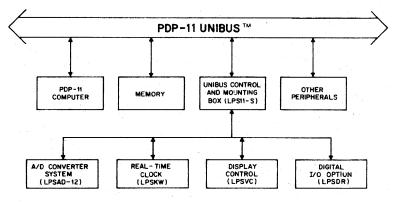

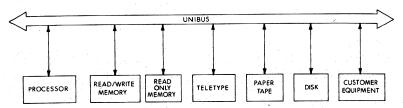

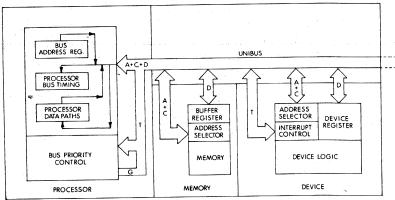

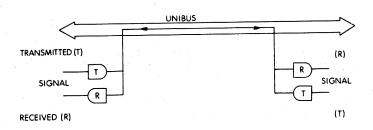

All computer system components and peripherals connect to and communicate with each other on a single high-speed bus known as the UNIBUS, see Figure 1-1.

Figure 1-1 PDP-11 System Block Diagram

The form of communication is the same for every device on the UNIBUS. The central processing unit (CPU) uses the same set of signals to communicate with main memory as with peripheral devices. Peripheral de-

vices also use this set of signals when communicating with the processor, memory or other peripheral devices. Each device, including memory locations, processor registers, and peripheral device registers, is assigned an address on the UNIBUS.

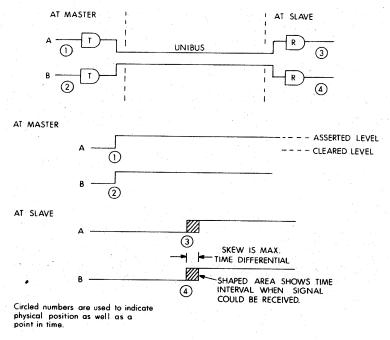

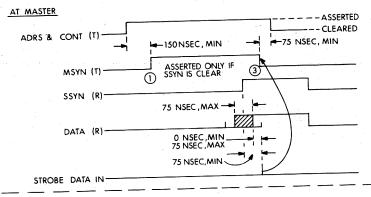

With bidirectional and asynchronous communications on the UNIBUS, devices can send, receive, and exchange data with minimum processor intervention. Because it is asynchronous, the UNIBUS is compatible with devices operating over a wide range of speeds. Interfaces to the UNIBUS are not time dependent; there are no pulse-width or rise-time restrictions.

Full 16-bit words or 8-bit bytes of information can be transferred on the bus. The information can be instructions, addresses, or data. Direct data transfers can occur between a peripheral device control and memory.

Refer to Chapter 5 for more detailed information about the UNIBUS and data transfers.

#### 1.6 CENTRAL PROCESSOR

The central processor, connected to the UNIBUS as a subsystem, controls the time allocation of the UNIBUS for peripherals and performs arithmetic and logic operations and instruction decoding. It contains multiple high-speed general-purpose registers which can be used as accumulators, address pointers, index registers, and other specialized functions. The processor can perform data transfers directly between input/output (I/O) devices and memory without disturbing the processor registers; does both single- and double-operand addressing and handles both 16-bit word and 8-bit byte data.

#### Instruction Set

The instruction complement uses the flexibility of the general-purpose registers to provide over 400 powerful hard-wired instructions. Unlike conventional 16-bit computers, which usually have three classes of instructions (memory reference instructions, operate or control instructions and I/O instructions) all operations in the PDP-11 are accomplished with one set of instructions. Since peripheral device registers can be manipulated as flexibly as core memory by the central processor, instructions that are used to manipulate data in core memory may be used equally well for data in peripheral device registers.

#### 1.7 SOFTWARE

The PDP-11 family of central processors and peripherals is supported by a comprehensive set of operating system software which allows the user to efficiently program his applications. System software is available to support small stand-alone configurations, disk based real-time and program development systems, and large scale multiprogramming and time-sharing systems. Some examples are:

- PAPER TAPE SYSTEM—Core only high speed paper tape configuration with program development in assembly language. Editor, debugger, and linker are supplied along with a relocating assembler.

- CASSETTE PROGRAMMING SYSTEM (CAPS-11)—Monitor based system with cassettes as a file structured medium. Interrupt driven program development system with relocating assembler, linker, editor,

debugger and peripheral interchange program. Can support BASIC as a higher level language processor.

- REAL TIME SINGLE USER SYSTEM (RT-11)—DECtape or DECpack disk based system for real time and program development. Features MACRO assembler, linker, editor, debugger, and peripheral interchange program. Supports BASIC with real time extensions as a higher level language.

- DISK BASED BATCH OPERATING SYSTEM (DOS/BATCH-11)—Disk based system with support for a full line of PDP-11 peripherals. Features interactive or BATCH mode of operation, sophisticated file handling and protection, powerful and flexible command language. Contains MACRO, editor, debugger, linker, librarian, peripheral interchange package, and file utility programs. Supports a powerful FORTRAN IV language processor and scientific package.

- ADVANCED REAL-TIME OPERATING SYSTEM (RSX-11D)—Modular disk based hardware protected multiprogramming systems featuring concurrent multiple real-time task execution and BATCH program development. Contains MACRO, editor, debugger, task builder, librarian, utilities and FORTRAN IV with real-time extensions.

- RESOURCE TIME SHARING SYSTEM (RSTS/E)—Disk based time sharing implementing BASIC-PLUS language, an enriched version of BASIC. Up to 32 simultaneous users via interactive terminals and sharing of system resources with spooling features. Complete file security and manipulation through utilities.

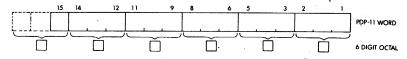

#### 1.8 PDP-11 WORD

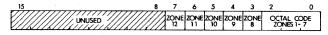

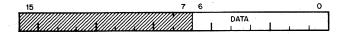

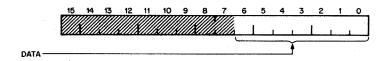

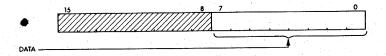

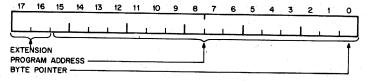

The 16-bit PDP-11 word can be represented conveniently as a 6-digit octal word. Bit 15, the Most Significant Bit (MSB), is used directly as the Most Significant Digit of the octal word. The other 5 octal digits are formed from the corresponding groups of 3 bits in the binary word. See Figure 1-2.

#### Octal Representation

Figure 1-2

When an extended address of 18 bits is used (shown later in the Handbook), the Most Significant Digit of the octal word is formed from bits 17, 16, and 15. For unsigned numbers, the correspondence between decimal and octal is:

| Decimal              | Octal   |                |

|----------------------|---------|----------------|

| 0                    | 000 000 |                |

| $(2^{16}-1)=65,535$  | 177 777 | (16-bit limit) |

| $(2^{18}-1)=262,143$ | 777 777 | (18-bit limit) |

#### **CHAPTER 2**

## **PROGRAMMING**

#### 2.1 GENERAL

Programming of peripherals is extremely simple in the PDP-11; a special class of instruction to deal with input/output operations is unnecessary. The UNIBUS permits a unified addressing structure in which control, status, and data registers for peripheral devices are directly addressed as memory locations. Therefore all operations on these registers, such as transferring information into or out of them or manipulating data within them, are performed by normal memory reference instructions.

The use of all memory reference instructions on peripheral device registers greatly increases the flexibility of input/output programming. For example, information in a device register can be compared directly with a value and a branch made on the result.

All peripheral device registers can be treated as accumulators. There is no need to funnel all data transfers, arithmetic operations, and comparisons through a single or small number of accumulator registers.

#### NOTE

A summary of the PDP-11 instruction set is contained in Appendix C. A brief description of the PDP-11 Assembly language is provided in Appendix D. Programming examples used throughout this Handbook are in Assembly language.

#### 2.2 ADDRESSES

#### Words and Bytes

Since the PDP-11 can operate on individual 8-bit bytes, a 16-bit word allows addressing 65,536 bytes ( $2^{16}=65,536$ ). It is common to refer to this as 64K, where K is equal to 1,024. Thus 64K bytes, or 32K 16-bit words are directly addressable. Actually in the PDP-11, the top 4K addresses are reserved for internal CPU registers and external input/output (I/O) registers. If all of the memory space were used, there could be 28K words of physical memory plus 4K locations for the CPU and I/O registers.

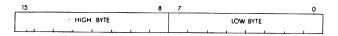

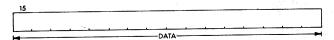

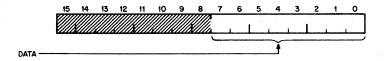

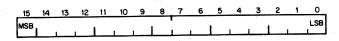

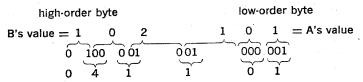

A PDP-11 word is divided into a high byte and a low byte as shown in Figure 2-1.

Figure 2-1 PDP-11 Word

Low bytes are stored at even numbered memory locations and high bytes are stored at odd numbered locations. Words always start at even numbered locations. **Expanded Addressing**

With the larger PDP-11 computers, expansion above 28K of memory can be achieved by using the Memory Management option. Memory Management provides an 18-bit effective memory address which permits addressing up to 124K words of actual memory.

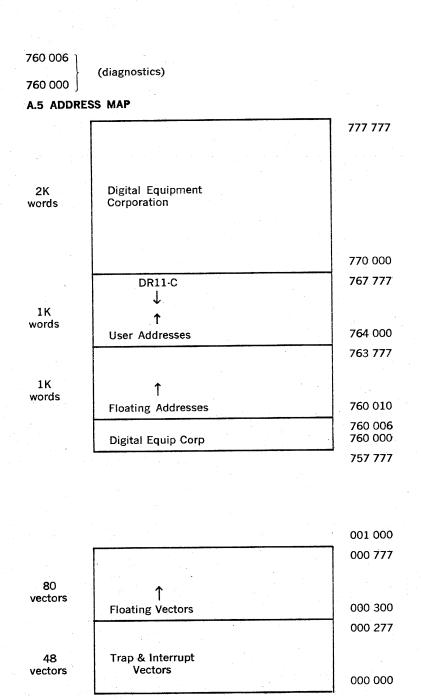

If the Memory Management option is not used, an octal address between 160 000 and 177 777 is interpreted as 760 000 to 777 777. That is, if bits 15, 14, and 13 are 1's, then bits 17 and 16 (the extended address bits) are considered to be 1's, which relocate the last 4K words (8K bytes) to become the highest locations accessed by the UNIBUS.

#### 2.3 DEVICE REGISTERS

All peripheral devices are specified by a set of registers which are addressed as main memory. There are two types of registers associated with each device:

- a) Control and status

- b) Data buffer

**Control and Status Registers**

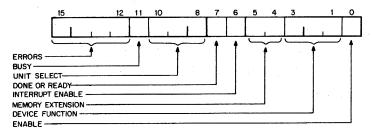

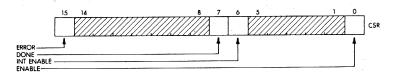

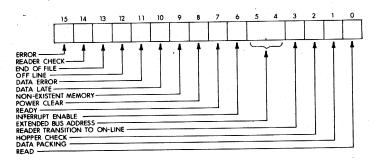

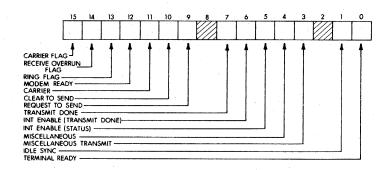

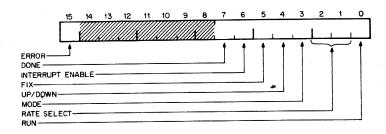

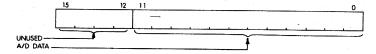

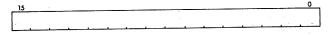

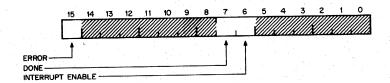

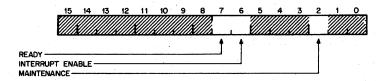

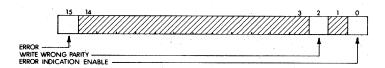

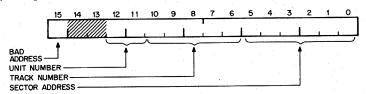

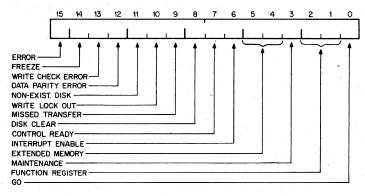

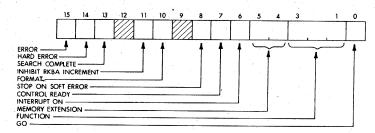

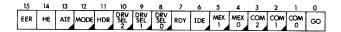

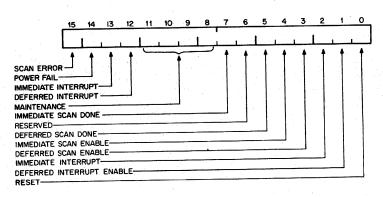

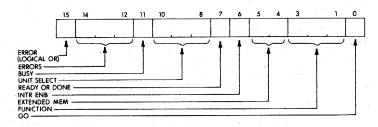

Each peripheral has one or more control and status registers that contain all the information necessary to communicate with that device. The general form, shown in Figure 2-2 does not necessarily apply to every device, but is presented as a guide.

Figure 2-2 Control & Status Register

Many devices require less than 16 status bits. Other devices will require more than 16 bits and therefore will require additional status and control registers.

The bits in the control and status registers are generally assigned as follows:

BIT NAME

15-12 Errors

#### **FUNCTION**

Generally there is an individual bit associated with a specific error. When more bits are required for errors, they can be obtained by expanding the error section in the word or by using another status word. Generally Bit 15 is the inclusive OR of all

|      |                      | other error bits (if there is more than one). Most devices will have "hard" error conditions which will cause an interrupt if bit 6 is set. Some may also have "soft" errors (warning types) which do not cause immediate interrupts. All errors are generally indicated by individual status bits. |

|------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11   | Busy                 | Set to indicate that a device operation is being performed.                                                                                                                                                                                                                                         |

| 10-8 | Unit Select          | Some peripheral systems have more than one device per control. For example, a disk system can have multiple surfaces per control and an analog-to-digital converter can have multiple channels. The unit bits select the proper surface or channel.                                                 |

| 7    | Done or Ready        | The register can contain a Done bit, a Ready bit or a Done-Busy pair of bits, depending on the device. These bits are set and cleared by the peripheral device, but may be queried by the program to determine the availability of the device.                                                      |

| 6    | Interrupt Enable     | Set by the program to allow an interrupt to occur as a result of a function done or error condition.                                                                                                                                                                                                |

| 5-4  | Memory Extension     | Allows devices to use a full 18 bits to specify addresses on the bus.                                                                                                                                                                                                                               |

| 3-1  | Device Function Bits | Specifies the operation that a device is to perform.                                                                                                                                                                                                                                                |

| 0    | Enable               | Set to enable the device to perform an operation.                                                                                                                                                                                                                                                   |

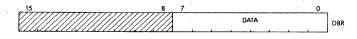

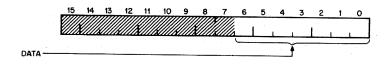

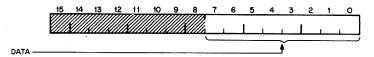

#### **Data Buffer Registers**

The data buffer register is used for temporarily storing data to be transferred into or out of the computer. The number and type of data registers is a function of the device.

#### 2.4 PROCESSOR REGISTERS

#### 2.4.1 General Registers

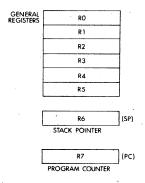

The central processor contains 8 general registers which can be used for a variety of purposes. The registers can be used as accumulators, index registers, auto-increment registers, auto-decrement registers, or as stack pointers for temporary storage of data. Arithmetic operations can be from one general register to another, from one memory or device register to another, or between memory or a device register and a general register. Refer to Figure 2-3.

R7 is used as the program counter (PC) and contains the address of the next instruction to be executed. It is a general register normally used only for addressing purposes and not as an accumulator for arithmetic operations.

Figure 2-3 General Registers

The R6 register is normally used as the Stack Pointer indicating the last entry in the appropriate stack (a common temporary storage area with "Last-in First-Out" characteristics).

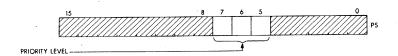

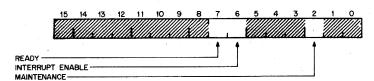

#### 2.4.2 Processor Status Word (PS) 777 776

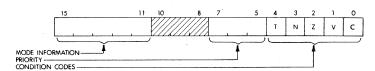

Figure 2-4 Processor Status Word

The Processor Status word, at location 777776, contains information on the current status of the computer. This information includes the condition codes describing the results of the last instruction; and an indicator for detecting the execution of an instruction to be trapped during program debugging, see Figure 2-4.

Bits 15 to 11 are used in the larger PDP-11 computers for operational mode information, and will not be covered in this Handbook. Refer to the 11/40 or 11/45 Handbooks for further information.

#### Processor Priority

The central processor operates at any one of eight levels of priority, 0-7. When the CPU is operating at level 7 an external device cannot interrupt it with a request for service. The central processor must be operating at a lower priority than the external device's request in order for the interruption to take effect. The current priority is maintained in the Processor Status word (bits 7-5), with bit 5 being the LSB. The 8 processor levels provide an effective interrupt mask.

#### **Condition Codes**

The condition codes contain information on the result of the last CPU operation.

The bits are set as follows:

Z = 1, if the result was zero

N = 1, if the result was negative

C=1, if the operation resulted in a carry from the MSB

V = 1, if the operation resulted in an arithmetic overflow

#### Trap

The trap bit (T) can be set or cleared under program control. When set, a processor trap will occur through location 14 on completion of instruction execution and a new Processor Status word will be loaded. This bit is especially useful for debugging programs as it provides an efficient method of installing breakpoints.

#### 2.5 INTERRUPT STRUCTURE

If the appropriate Interrupt Enable bit is set in the control and status register of a device, transition from 0 to 1 of the Ready or Error bit causes an interrupt request to be issued to the processor. Also if Ready or Error is a 1 when the Interrupt Enable is turned on, an interrupt request is made. If the device makes the request at a priority greater than that at which the processor is running and no other conflicts exist, the request is granted and the interrupt sequence takes place:

- a) the current program counter (PC) and processor status (PS) are pushed onto the processor stack;

- b) the new PC and PS are loaded from a pair of locations (the interrupt vector) in addressed memory, unique to the interrupting device.

Since each device has a unique interrupt vector which dispatches control to the appropriate interrupt handling routine immediately, no device polling is required. Furthermore, since the PS contains the processor priority, the priority at which an interrupt request is serviced can be set under program control and is independent of the priority of the interrupt request. The Return from Interrupt Instruction is used to reverse the action of the interrupt sequence. The top two words on the stack are popped into the PC and PS, returning control to the interrupted sequence.

#### 2.6 PROGRAMMING WITH DEVICE REGISTERS

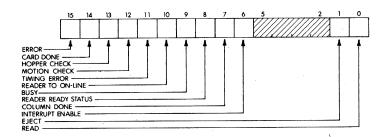

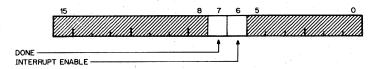

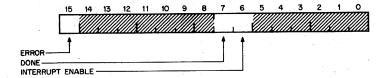

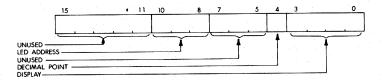

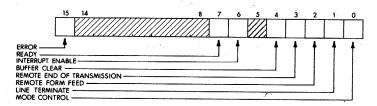

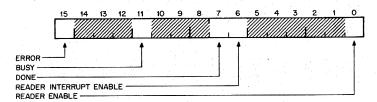

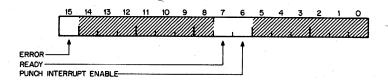

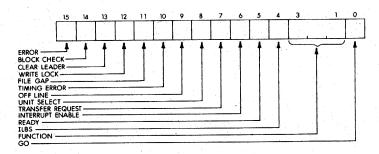

The diagram of Figure 2-5 shows 4 bits that would appear in many common Command and Status registers.

Figure 2-5 CSR Register

| BIT | NAME                           | FUNCTION                                                                                                             |

|-----|--------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 15  | Error                          | Set when an error occurs.                                                                                            |

| 7   | Done                           | Set when the device is either ready to accept new information, or has completed an operation and has data available. |

| 6   | Interrupt Enable<br>(INT ENBL) | When set, an interrupt will be requested when Done or Error becomes a 1.                                             |

| 1   | Device Enable (ENBL)           | Set to allow the peripheral device to perform a function.                                                            |

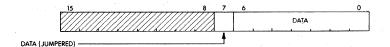

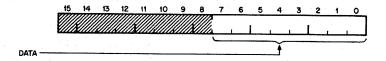

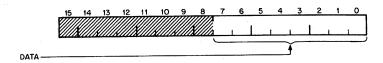

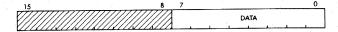

The diagram of Figure 2-6 shows a typical data buffer that can hold an 8-bit character.

Figure 2-6 DBR Register

| BIT | NAME | FUNCTION                                                                              |

|-----|------|---------------------------------------------------------------------------------------|

| 7-0 | Data | Holds the ASCII code for a character to be either written to or read from the periph- |

|     |      | eral device.                                                                          |

In the following examples, these two registers will be referred to by the symbolic designations, CSR and DBR.

**Example:** Transfer information from the peripheral data buffer to general register R3.

#### MOV DBR, R3

Since the information is only 8 bits, and it resides in the low part of the DBR, the byte instruction would accomplish the same purpose;

#### MOVB DBR, R3

The bit manipulating instructions,

BIT (bit test), set condition codes N & Z according to an AND operation on corresponding bits; neither source nor destination are modified.

BIC (bit clear), put 0's in all positions of the destination that correspond to a 1 in the source.

BIS (bit set), put 1's in all positions of the destination that correspond to a 1 in the source (OR operation).

can be used to conveniently modify or test the contents of the CSR register.

**Example:** Enable the peripheral device to perform an I/O function:

BIS #1, CSR ; OR CODE 000 001 WITH THE CSR

This instruction will set bit 0 of the CSR, but leave all other bits unchanged.

**Example:** Test for an error, and branch to an error handling routine if there is an error.

TST CSR ;SET CONDITION CODE BITS ON CONTENTS OF CSR

BMI ERRTN :TEST BIT 15, BRANCH ON MINUS

ERRTN means the address of the error routine. When there is an error, bit 15 = 1, the CSR looks like a negative number (sign bit = 1).

**Example:** Test to see if the peripheral device has performed a read function, and data is available. Transfer to a read subroutine if data is available.

BIT #200, CSR

:TEST BIT 7 OF THE CSR

BNE SBR

:BRANCH IF DONE IS SET

The CSR register is ANDed with a word of all 0's except for bit 7. If bit 7 (DONE) of the CSR is a 1, the result is not zero, and a branch on not equal to 0 can be made to a service subroutine (SBR).

Example: Prevent the peripheral device from causing an interrupt.

BIC #100, CSR

:CLEAR THE INT ENBL BIT

Using a source of 000 100 has the effect of clearing bit 6 (INT ENBL), but leaving all other bits of the CSR alone.

Example: Have the program continuously check the DONE bit, and read a word when it becomes a 1.

AGAIN: TSTB CSR

TEST BIT 7, SIGN BIT

BPL AGAIN

:BRANCH IF NOT SET

MOVB DBR, RO

:TRANSFER DATA TO CPU

Bit 7 of the CSR is conveniently the sign bit for the low order byte, and can be tested directly by a single instruction.

#### 2.7 DEVICE PRIORITY

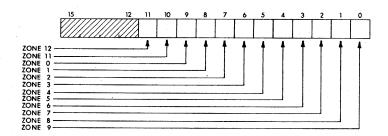

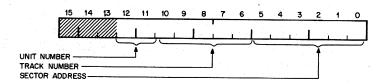

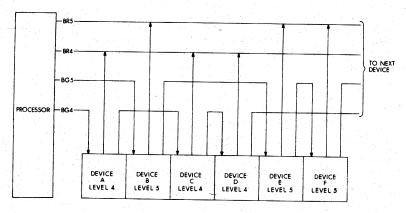

Each peripheral has a priority level assigned to it by hardware, allowing it to interrupt lower priority level devices. To ensure that the CPU which executes the peripheral's service routine is not incorrectly interrupted, the CPU itself must take on the priority level of the interrupting peripheral (Level 4, 5, 6, or 7) while running the service routine, see Figure 2-7.

Figure 2-7 Processor Status Word

**Example:** Write a program to service the input keyboard data (register KBB) from the LA30 DECwriter. The interrupt vector is at location 60, and the priority level is 4.

= 60

.WORD KBSBR ;PC = KEYBOARD SUBR ADDRESS . WORD 200 ;PS = 4 (BITS 7, 6, 5, = 100)

KBSBR; MOV KBB. R1

RTI

Example: Set the priority level of the processor to level 3.

PS = 777776 ;ADDRESS OF PROC STATUS WORD

CLR PS ;START WITH ALL 0's BIS #140, PS ;SET BITS 6 & 5, PS = 3

**Example:** A paper tape reader interrupt service could appear as follows: First the user must initialize the service routine by specifying an address pointer and a word count

INIT: MOV #BUFADR, POINTR ;SET ADDRESS POINTER

MOV #COUNT, COUNTR ;SET COUNTER

MOV #101,PRS ;ENABLE READER PROGRAM TO CON-

;TINUE UNTIL INTERRUPT

When the interrupt occurs and is acknowledged, the processor stores the current PC and PS on the stack. Next it goes to the interrupt vector and picks up the new PC and PS beginning at location 70. When the program was loaded the address of PRSER, the PR service routine, would be put in location 70 and 200<sub>8</sub> in 72 (to set priority at 4). The next instruction executed is the first instruction of PRSER.

PRSER: TST PRS ;TEST FOR ERROR

BMI ERROR ;BRANCH IF BIT 15 SET

MOVB PRB,@POINTR ;MOVE CHARACTER TO BUFFER

INC POINTR ;INCREMENT POINTER

DEC COUNTR ;DECREMENT CHARACTER COUNT

BEQ DONE ;BRANCH WHEN INPUT DONE

INC PRS ;START READER FOR NEXT CHARAC-

;TER

DONE: RTI ;RETURN TO INTERRUPTED PRO-

;GRAM

## CATEGORIES OF PERIPHERALS

#### 3.1 GENERAL

This chapter contatins general information and comparisons of the PDP-11 peripherals. Sometimes a peripheral will fall into more than one category, and it will be listed wherever applicable.

This chapter shows the broad range of peripheral equipment offered and the wide span of equipment capabilities. Some of them are compared below.

#### Comparison of Input Equipment

| MEDIUM        | PRODUCT                                          | INPUT SPEED (max)        |

|---------------|--------------------------------------------------|--------------------------|

| Paper tape    | Teletype, LT33<br>High speed reader/punch, PC11  | 10°characters/sec<br>300 |

| Cards         | Card reader, CD11                                | 1,600                    |

| Magnetic tape | Cassette, TA11<br>DECtape, TC11<br>Magtape, TM11 | 560<br>10,000<br>36,000  |

## Comparison of Output Equipment

| MEDIUM        | PRODUCT                                                 | OUTPUT SPEED (max)      |

|---------------|---------------------------------------------------------|-------------------------|

| Paper tape    | Teletype, LT33<br>High speed reader/punch, PC11         | 10 characters/sec<br>50 |

| Printer       | Teletype, LT33<br>DECwriter, LA30<br>Line printer, LP11 | 10<br>30<br>2,600       |

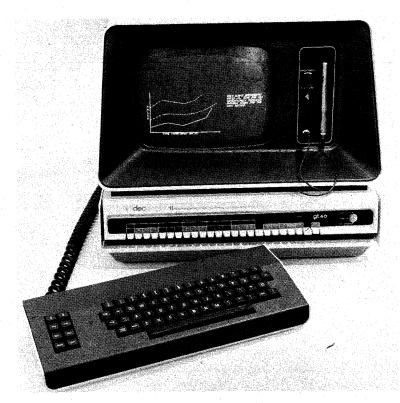

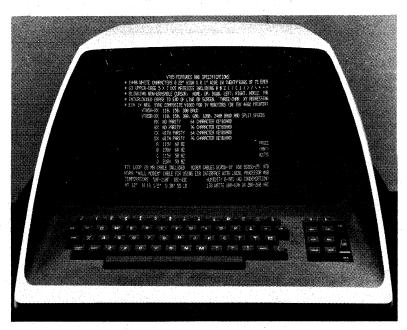

| CRT terminal  | Alphanumeric terminal, VT05<br>Graphic terminal, GT40   | 240<br>960              |

| Magnetic tape | Cassette, TA11<br>DECtape, TC11<br>Magtape, TM11        | 560<br>10,000<br>36,000 |

#### 3.2 MAIN MEMORY

#### 3.2.1 General

Memories with different ranges of speeds and various physical and electrical characteristics can be freely mixed and interchanged within a PDP-11 system. Memory is treated as a physically modular, but electrically integral part of the computing system.

Types of Memory

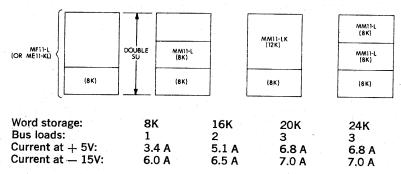

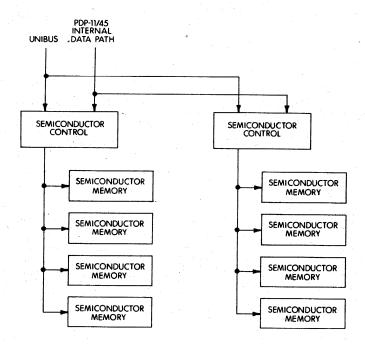

Core, semiconductor, and read only memory (ROM) is offered for PDP-11 systems. Although semiconductor memory (MOS and bipolar) can be used only with the PDP-11/45, all other memories can be used with any PDP-11 Central Processing Unit.

Parity is an available option for both core and semiconductor memory. No increase in mounting space is required.

#### **Operating Speed**

The CPU can begin processing data immediately after accessing it. (Access time is defined as the time interval between request and when the data is available.) Core memory then rewrites itself while the processor is working. (Semiconductor memory contents are not destroyed on read-out.) This makes the access time the important operating parameter for the PDP-11, thus providing increased speed and efficiency. The only effect cycle time has on the PDP-11 is the time needed between successive transfers to memory.

#### **Packaging**

Memory is offered as a complete system, including control and interfacing logic, interconnecting cables, and mounting assembly. Several of the PDP-11 processors have dedicated, pre-wired areas within the chassis for holding additional memory. In other cases, memory can be added within the CPU mounting assembly, and the necessary power taken from the cabinet power supplies. A separate, self-contained memory unit is available that includes its own power supply and rack-mountable assembly unit.

#### Modes of Operation

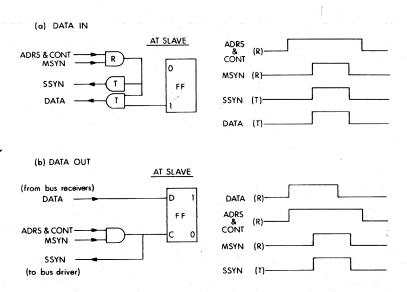

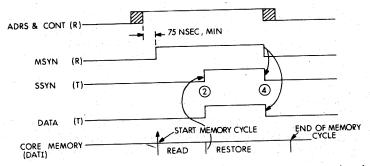

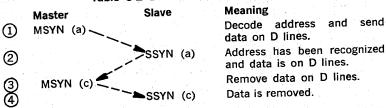

Read (DATI)—A complete memory cycle is performed, and the contents of core are restored after being read. Transfer is Data In (to the UNIBUS or the CPU). In the master-slave relationship on the bus, memory is always the slave.

Read/Pause (DATIP)—Split cycle operation. Data read from core is not restored because new data is to be entered. This operation must be followed by a write cycle (DATO or DATOB) to the accessed location.

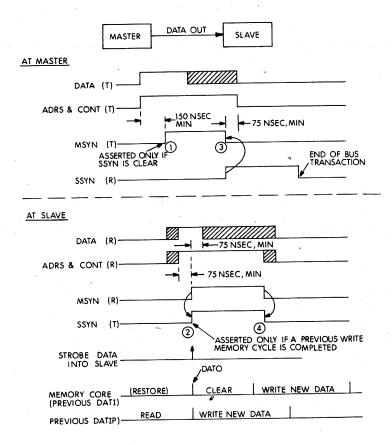

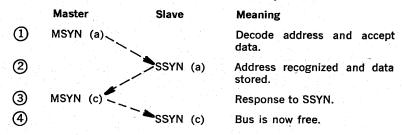

Write (DATO)—A full 16-bit word is loaded into memory. Transfer is Data Out (from the UNIBUS or the CPU).

Write Byte (DATOB)—An 8-bit byte is loaded; otherwise it is the same operation as DATO.

#### 3.2.2 Products

| MODEL  | DESCRIPTION      | ACCESS TIME | CYCLE TIME |

|--------|------------------|-------------|------------|

| MM11   | Core memory      | 360 nsec    | 900 nsec   |

| MS11-B | MOS memory       | 350         | 450        |

| MS11-C | Bipolar memory   | 200         | 300        |

| BM792  | Read only memory | 100         |            |

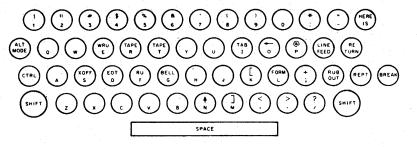

#### 3.3 TERMINALS

#### **Characteristics and Applications**

- a) convenient human interface to the computer

- b) typewriter-like keyboard for data entry

- c) printer or display for output from computer

- d) basic input/output device

- e) can be local (console terminal), or remote

#### **Products**

| MODEL                        | DESCRIPTION                                                                  | OUTPUT SPEED (max)                                                                   |

|------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| LT33<br>LA30<br>VT05<br>GT40 | Teletype DECwriter Alphanumeric Graphic display system (includes a computer) | 10 characters/sec 30 240 960 char/sec as a simple serial interfaced terminal, opera- |

|                              |                                                                              | tion can be faster as a syn-                                                         |

chronous device

#### 3.4 PAPER TAPE

#### **Characteristics and Applications**

- a) simple medium to use

- b) separate tapes for individual programs

- c) variable program length

- d) data can be read by a person

#### **Products**

| LT33 Teletype terminal 10 char/sec 10 char/sec PC11 Paper tape reader/punch 300 50 PR11 Paper tape reader 300 | MODEL | DESCRIPTION             | READ SPEED | PUNCH SPEED |

|---------------------------------------------------------------------------------------------------------------|-------|-------------------------|------------|-------------|

|                                                                                                               | PC11  | Paper tape reader/punch | 300        |             |

#### 3.5 CARDS

### **Characteristics and Applications**

- a) individual records

- b) easy to add, delete, or rearrange a card

- c) possible to print on the card

- d) can be read by a person

#### **Products**

| MODEL                | DESCRIPTION                               | TYPE                                  | READ SPEED                   |

|----------------------|-------------------------------------------|---------------------------------------|------------------------------|

| CM11<br>CR11<br>CD11 | Card reader<br>Card reader<br>Card reader | mark-sense or punch<br>punch<br>punch | 285 cards/min<br>300<br>1200 |

#### 3.6 PRINTERS

#### Characteristics and Applications

- a) hard copy for permanent records

- b) impact types can make multiple copies

- c) some plotting capability

#### **Products**

| MODEL                        | DESCRIPTION                                           | TYPE                                 | PRINT SPEED                                                            | COLUMNS                         | CHAR.                         |

|------------------------------|-------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------|---------------------------------|-------------------------------|

| LT33<br>LA30<br>LS11<br>LP11 | Teletype<br>DECwriter<br>Line printer<br>Line printer | impact<br>impact<br>impact<br>impact | 10 char/sec<br>30 char/sec<br>60 lines/min<br>170 to 1200<br>lines/min | 64<br>80<br>132<br>80 or<br>132 | 64<br>64<br>62<br>64 or<br>96 |

| LV11                         | Printer/plotter                                       | electro-                             | 500 lines/min                                                          | 132                             | 96                            |

#### 3.7 MAGNETIC TAPE

## **Characteristics and Applications**

- a) unlimited off-line storage

- b) removable medium

#### **Products**

| MODEL     | DESCRIPTION                                          | STORAGE/REEL | DATA RATE    |

|-----------|------------------------------------------------------|--------------|--------------|

| TA11      | Cassette DECtape Magnetic tape (industry compatible) | 90,000 char  | 560 char/sec |

| TC11/TU56 |                                                      | 255,000      | 10,000       |

| TM11/TU10 |                                                      | 20,000,000   | 36,000       |

#### 3.8 DISKS

#### **Characteristics and Applications**

- a) fast access to on-line storage

- b) swapping programs

- c) virtual memory

- d) efficient bulk storage

- a) Fixed Head-fast access time

- b) Moving head—high storage capacity, more economical storage

- c) Disk pack-removable medium, unlimited off-line storage

The average access time (avg latency) is equal to  $\frac{1}{2}$  the time for a revolution plus the average head positioning time (for moving head disks only).

#### **Products**

| MODEL     | DESCRIPTION     | CAPACITY/<br>DRIVE | AV ACCESS<br>TIME | DATA RATE    |

|-----------|-----------------|--------------------|-------------------|--------------|

|           | Fixed head disk | 64 K words         | 17 msec           | 16 μsec/word |

| RF11/RS11 | Fixed head disk | 256 K              | 17                | 16           |

| RK11/RK05 | Disk cartridge  | 1.2 million        | 70                | 11           |

| RP11/RP03 | Disk pack       | 20 million         | 42                | 7.5          |

#### 3.9 DISPLAYS

#### **Characteristics and Applications**

- a) pleasing human interface

- b) soft copy of information

- c) fast presentation of information

- d) alphanumeric and graphic capability

#### Products

MODEL DESCRIPTION VR01 Oscilloscope Point plot display VR14 Storage display VT01 VT05 Alphanumeric terminal GT40 Graphic display system (includes a computer)

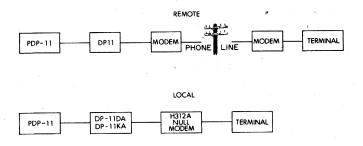

#### 3.10 COMMUNICATIONS OPTIONS Characteristics and Applications

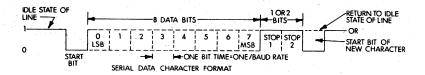

Asynchronous Interfaces—Character transmission time is variable, but bits within the character are timed; a character transmission normally includes a start bit, several data bits, one or more stop bits, and an optional parity bit.

Synchronous Interfaces-Continuous data stream once the receiver is synchronized; data is generally transmitted in message blocks containing both information and timing signals.

Other Communications Options-Provide error detection, autocalling unit interfacing, and signal conditioning.

| Products |                                                    |                                                                                                                            |

|----------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| MODEL    | DESCRIPTION                                        | TYPICAL USE                                                                                                                |

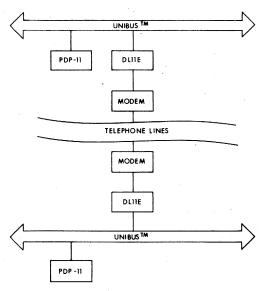

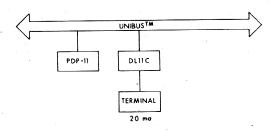

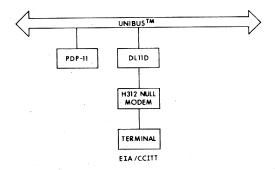

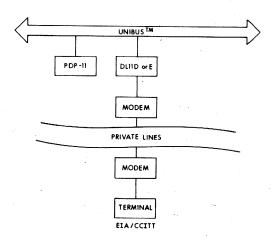

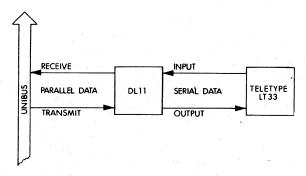

| DL11     | Single Asynchronous Line Interface                 | Connects PDP-11 to local terminals (such as Teletype, LA30 and VT05) or to remote terminals via modems.                    |

| DC11     | Dual Asynchronous Line<br>Interface (Programmable) | Connects PDP-11 to remote terminals via modems. Transmission speed and other parameters may be changed by software.        |

| DJ11     | 16-Line Asynchronous<br>Multiplexer                | Connects PDP-11 to up<br>to 16-local terminals or<br>up to 16-remote ter-<br>minals via modems.<br>Transmission speeds and |

Connects PDP-11 to up 16-Line Programmable DH11 to 16-local terminals or Asynchronous Multiplexer remote terminals. Trans-

missions speeds and parameters are program-

other parameters are switch or jumper selectable in 4-line groups.

mable.

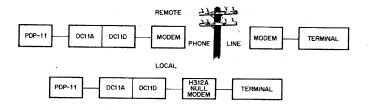

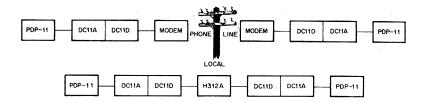

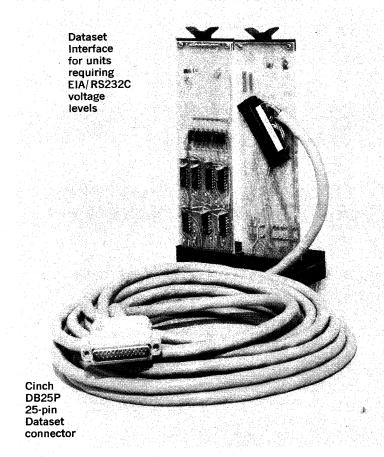

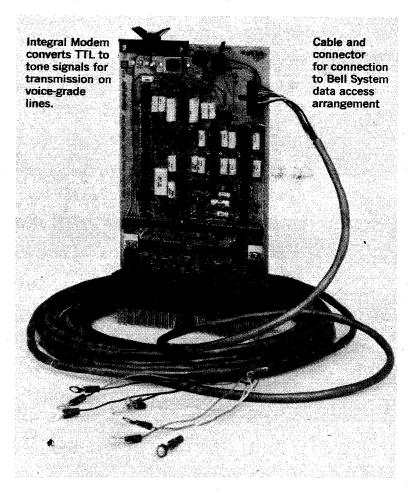

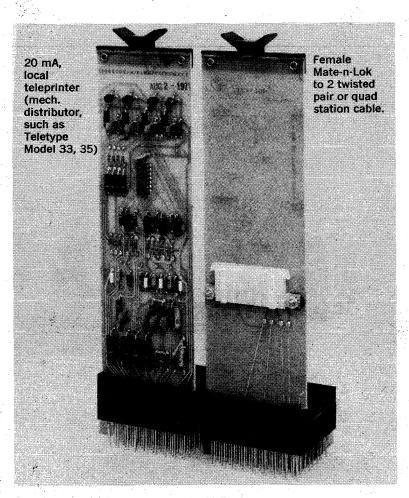

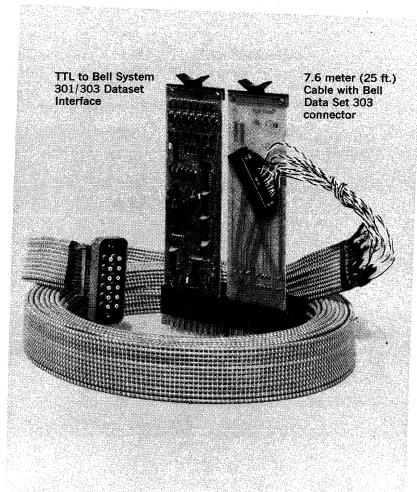

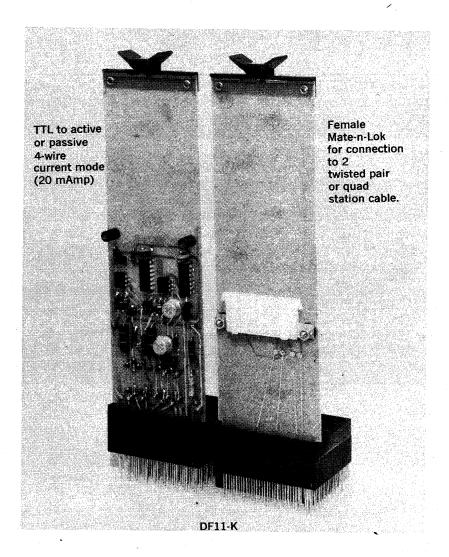

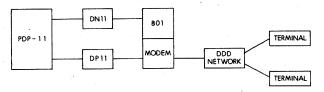

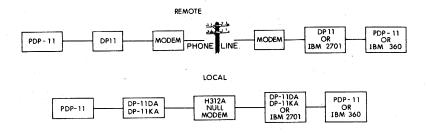

DP11 Single Line Asynchronous. Connects PDP-11 to Interface modems or communications for high speed transmissions. Can be used in computer-to-computer communications. KG11 Communication Arithmetic Used to detect errors in Flement serially transmitted data. DC08 and H316 Telegraph Line Interfaces Connect PDP-11 to telegraph equipment. DF11 Signal Conditioning Options Convert computer (TTL) signals to EIA or 20 ma signals. Can be used with DC11, DL11 and DH11 interfaces. DF11-B Integral Modems Convert TTL signals to audio frequencies. Used to connect PDP-11 directly to Bell Data Access Arrangement options. DF01 Acoustic Coupler Connects terminal (VT05, LA30) to standard telephone for communication with computer via phone lines. H313-A Voltage Current Adapter Converts Digital supplied TTY output for use with Bell 103 modems or equivalent. H312-A Null Modem Allows direct connection of a terminal with an FIA cable to a DC11, DP11.

#### 3.11 DATA ACQUISITION

#### Characteristics and Applications

- a) analog conversion equipment

- b) analog circuitry

- c) digital control and monitoring

- d) timing control

- e) laboratory experimentation

- f) industrial control

#### **Products**

MODEL DESCRIPTION

AA11 Digital-to-analog conversion subsystem, 12 bits

AD01 Analog-to-digital conversion subsystem, 10 or 11 bits

DL11, or DM11-DB.

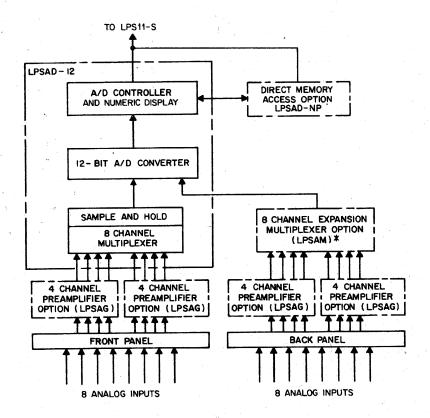

| LPS11  | Lab Peripheral System, 12 bits (A/D, real time clock, D/A, digital I/O) |

|--------|-------------------------------------------------------------------------|

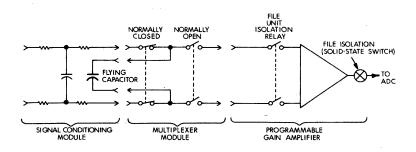

| AFC11  | Low level analog input subsystem, flying capacitor scanner              |

| UDC11  | Digital control subsystem                                               |

| KW11-L | Line clock                                                              |

| KW11-P | Programmable clock                                                      |

## 3.12 UNIBUS EQUIPMENT

| MODEL                                        | DESCRIPTION                                                                                                                               |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| DR11-C<br>DR11-B<br>DT03<br>DA11-B<br>DA11-F | General device interface (program interrupts) Direct Memory Access interface (NPR data transfers) UNIBUS switch UNIBUS link UNIBUS window |

## 3.13 MOUNTING EQUIPMENT

| MODEL                                                            | DESCRIPTION                                                                                                                                           | SYSTEM UNIT            | SPACE |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------|

| BB11<br>DD11<br>BA11-ES<br>H960-D<br>H960-E<br>H960-CA<br>H961-A | Blank mounting panel Peripheral mounting panel Extension Mounting Box Cabinet with a drawer Cabinet with 2 drawers Cabinet Cabinet without end panels | 1<br>1<br>6<br>9<br>18 |       |

## **DESCRIPTIONS OF PERIPHERALS**

#### 4.1 INTRODUCTION

This chapter contains detailed descriptions, specifications, programming, and operating information for PDP-11 peripheral equipment. For ease of reference, the peripherals have been arranged alphanumerically by model number, with the model number appearing on the top right-hand side of each page.

Since some peripherals have similar descriptions and specifications, related peripherals will be described within the same section. Section 4.3 contains a complete list of all equipment described in this chapter. Appendix E contains an index to all equipment described in this Handbook.

#### 4.2 EXPLANATION OF TERMS AND SPECIFICATIONS .

#### 4.2.1 Products

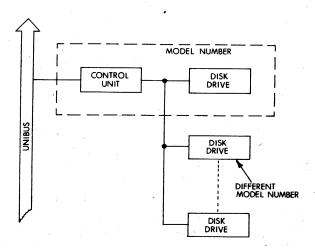

All the peripherals mentioned in this chapter must eventually interface to the UNIBUS. Some of the equipment, such as Line Printers, include a control unit as well as the printer itself. The control unit, sometimes referred to as a controller or interface unit, is the actual logic equipment between the UNIBUS and the peripheral device. With terminals, the control unit and the terminal itself are separate products. In this case, several different control units could be used, depending on the application. In other cases, such as disk drives, a single model number includes a control unit and the first disk drive of the system. Other disk drives, up to the limit of the system, are specified by another model number, see Figure 4-1.

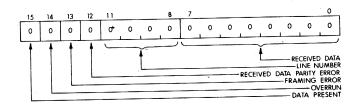

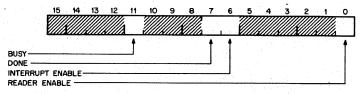

#### 4.2.2 Registers

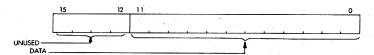

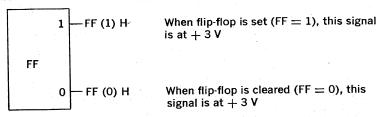

The device registers are shown with their common name, their mnemonic in parentheses, then their UNIBUS address. Note that these addresses begin with 77 or 76 (instead of 17 or 16) to indicate that they are in the highest 4K words of address space. Within the functional description of each bit, if not otherwise indicated, the condition or operation when the bit is set (logic 1) is described.

Some bit positions of the registers are not used (not implemented with hardware). When diagrams are shown, unused positions are indicated by cross-hatching. Some of the bits are controlled only by the peripheral device and are indicated as read only (by the program). Some of the bits are write only (by the program), and are always read as zeros. Some bits are cleared (or set) by the UNIBUS master clear signal called Initialize, which has the mnemonic INIT. It is issued by turning Power ON, Console START, or the RESET instruction. Figure 4-2 summarizes the information about the device registers.

Figure 4-1. Disk Storage System

The unused or write only bits are always read as zeros by the program. Trying to load unused or read only bits has no effect on the addressed register.

#### Register (REG) 77x xxx

#### $\square = unused bit$

Read only: (with respect to the CPU or bus master)—The program can monitor the bit, but cannot modify it.

Write only: (with respect to the CPU or bus master)—The program can set or clear the bit; but when reading, it will always appear to be a zero.

Figure 4-2. Device Register

## 4.2.3 Specifications

#### **UNIBUS** Interface

Interrupt and trap vectors are assigned to the lowest part of memory, generally in the range 000 000 to 000 377. Bus Request (BR) levels are indicated; also Non-Processor Request (NPR) operation if applicable. Most devices that interface to the UNIBUS represent only 1 bus load.

#### Mechanical

The mounting arrangement of the equipment is indicated as:

| plugs into a dedicated logic module slot         |

|--------------------------------------------------|

| fits in a small peripheral controller slot       |

| (quad module)                                    |

| system unit mounting assembly is included        |

| uses front panel space in a cabinet              |

| suitable for placing on top of a table or a desk |

| by itself, not in a cabinet                      |

| mounts in a standard PDP-11 cabinet              |

|                                                  |

Some peripherals include 2 separate physical parts and are indicated by use of a plus (+) sign.

#### **Relative Humidity**

All humidity specifications mean without condensation.

#### **Temperature**

Correspondence between Centigrade and Fahrenheit is shown in the following table:

| °C | °F         | • .                                                 |

|----|------------|-----------------------------------------------------|

| 0  | 32         |                                                     |

| 5  | 41         |                                                     |

| 10 | 50         | Г 9]                                                |

| 15 | 59         | $(^{\circ}C) \times \frac{3}{5} + 32 = (^{\circ}F)$ |

| 20 | 68         | [ <u>5</u>                                          |

| 25 | 77         |                                                     |

| 30 | 86         |                                                     |

| 35 | <b>9</b> 5 |                                                     |

| 40 | 104        |                                                     |

| 45 | 113        |                                                     |

| 50 | 122        |                                                     |

| 55 | 131        | •                                                   |

|    |            |                                                     |

#### 4.2.4 Conversion Factors

(inches)

$$\times$$

2.54 = (cm)

(lbs)  $\times$  0.454 = (kg)

(Watts)  $\times$  3.41 = (BTU/hr)

#### 4.3 LIST OF PERIPHERALS

The peripherals described in this chapter are arranged in the following sequence:

| Model Numbers     | Description                | Page |

|-------------------|----------------------------|------|

| AA11 (also BA614) | D/A subsystem              | 4-5  |

| AD01              | A/D subsystem              | 4-9  |

| AFC11             | Low level analog subsystem | 4-13 |

| BA11 (also H720)  | Extension mounting box     | 4-19 |

| BB11              | Blank mounting panel       | 4-21 |

|                      | *                                     |                       |  |

|----------------------|---------------------------------------|-----------------------|--|

|                      |                                       |                       |  |

|                      |                                       |                       |  |

|                      | •                                     |                       |  |

| _                    |                                       |                       |  |

| BM792 (also MR11 DB, |                                       |                       |  |

| M792)                | Read only memory                      | 4-22                  |  |

| CD11                 | Punched card reader                   | 4-24                  |  |

| CR11 (also CM11)     | Punched card reader                   | 4-37                  |  |

| DA11-B               | UNIBUS link                           | 4-46                  |  |

| DA11-F               | UNIBUS window                         | 4-51                  |  |

| DB11                 | Bus repeater                          | 4-59                  |  |

| DC11                 | Asynch serial line interface          | 4-60                  |  |

| DD11                 | Peripheral mounting panel             | 4-68                  |  |

| DF01                 | Acoustic telephone coupler            | 4-72                  |  |

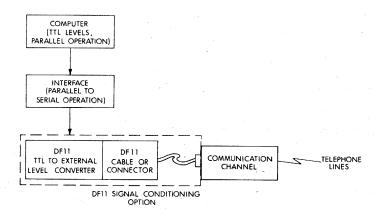

| DF11                 | Serial line signal conditioning       | 4-74                  |  |

| DH11 (also DM11)     | Asynch serial line multiplexer (prog) | 4-82                  |  |

| DJ11                 | Asynch serial line multiplexer        | 4-107                 |  |

| DL11                 | Single asynch serial line interface   | 4-124                 |  |

| DN11                 | Automatic calling unit interface      | 4-141                 |  |

| DP11                 | Synchronous interface                 | 4-149                 |  |

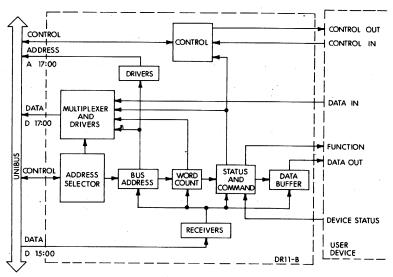

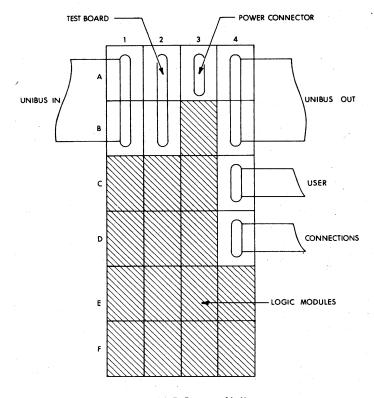

| DR11-B               | Direct memory access interface        | 4-160                 |  |

| DR11-C               | General device interface              | 4-165                 |  |

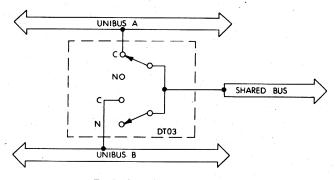

| DT03                 | UNIBUS switch                         | 4-175                 |  |

| GT40                 | Graphic display system                | 4-179                 |  |

| H312                 | Asynchronous null modem               | 4-185                 |  |

| H960 (also H961)     | Standard PDP-11 cabinet               | 4-186                 |  |

| KG11                 | Communications arithmetic option      | 4-188                 |  |

| KW11-L               | Line time clock                       | 4-197                 |  |

| KW11-P               | Programmable real time clock          | 4-198                 |  |

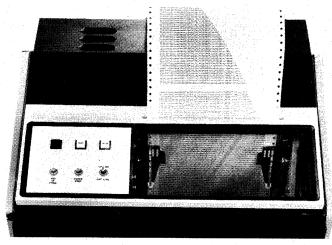

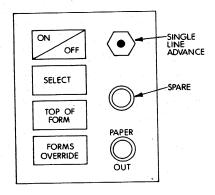

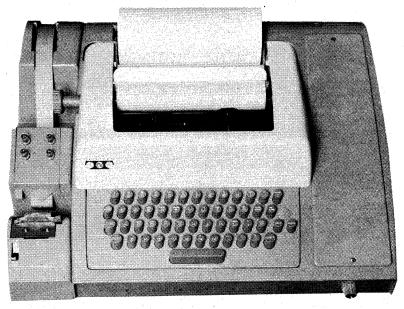

| LA30 (also LC11)     | DECwriter                             | 4-201                 |  |

| LP11                 | High speed line printer               | 4-208                 |  |

| LPS11                | Lab peripheral system                 | 4-218                 |  |

| LS11                 | Line printer                          | 4-227                 |  |

| LT33                 | Teletype terminal                     | 4-233                 |  |

| LV11                 | Electrostatic printer/plotter         | 4-241                 |  |

| MM11 (also MF11,     |                                       |                       |  |

| ME11)                | Core memory                           | 4-245                 |  |

| MS11                 | Semiconductor memory                  | 4-249                 |  |

| PC11 (also PR11)     | High speed paper tape reader/punch    | 4-252                 |  |

| RC11 (also RS64)     | DECdisk                               | 4-260                 |  |

| RF11 (also RS11)     | Fixed head disk                       | 4-272                 |  |

| RK11 (also RK05)     | DECpack disk cartridge                | 4-282                 |  |

| RP11 (also RP03)     | Disk pack                             | 4-294                 |  |

| TA11                 | Cassette                              | 4-304                 |  |

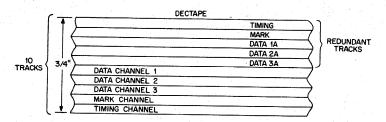

| TC11 (also TU56)     | DECtape                               | 4-309                 |  |

| TM11 (also TU10)     | Magnetic tape                         | 4-322                 |  |

| UDC11                | Universal digital control subsystem   | <b>4-</b> 33 <b>6</b> |  |

| VR01                 | Oscilloscope                          | 4-343                 |  |

| VR14                 | Point plot display                    | 4-344                 |  |

| VT01                 | Storage display                       | 4-345                 |  |

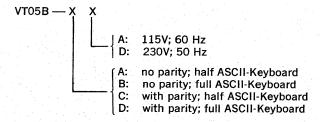

| VT05                 | Alphanumeric display terminal         | 4-346                 |  |

## DIGITAL TO ANALOG SUBSYSTEM, AA11-D

#### DESCRIPTION

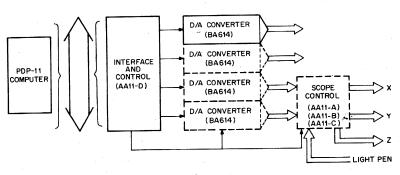

The AA11-D is a low cost, high performance multichannel digital-toanalog conversion subsystem for PDP-11 computers.

Interfacing directly to the PDP-11 UNIBUS, the AA11-D controls up to four single buffered, 12-bit bipolar digital-to-analog converters. Each BA614 converter, which includes output amplifier and reference voltage source, is contained on a plug-in module and provides 10 ma current output at  $\pm$  10 volts. Full scale output voltage is trimpot adjustable from  $\pm$  1y to  $\pm$  10v in two ranges.

Storage scope, display scope, and light pen control options are available for the AA11-D. These options provide Z axis blanking for intensity control and require two D/A converters to control X and Y trace coordinates.

Available as a factory or field installed option, the AA11-D fully implemented with four digital to analog converters and a scope control option, is contained in a single System Unit. A rack mountable power supply is separate.

AA11-D Subsystem

#### **REGISTERS**

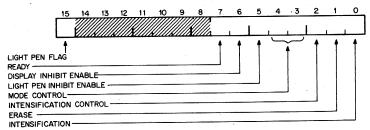

Command and Status Register (CSR) 776 756

| BIT | NAME                     | FUNCTION                                                                                                                                                                                                    |

|-----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15  | Light Pen Flag           | If bit 05 is "1," light pen flag causes interrupt. Cleared by INIT and reading the register. Read only.                                                                                                     |

| 7   | Ready                    | Set when scope is ready for service, because of INTEN or ERASE commands or X or Y has been loaded. Interrupt occurs if bit 06 is "1." Bit 07 is set by INIT and cleared by displaying new point. Read only. |

| 6   | Display Inhibit Enable   | Set to permit interrupts to occur when intensification or erasure is completed. This bit is set by program control and cleared by INIT. Read/Write.                                                         |

| 5   | Light Pen Inhibit Enable | Set to permit interrupts to occur when signal is received from light pen. This bit is set by program control and cleared by INIT. Read/Write.                                                               |

| 4-3 | Mode Control .           | Determines intensification on loading X or Y.                                                                                                                                                               |

| 2   | Intensification Control  | Selects Stored Mode or High Intensity<br>Mode depending on scope used.<br>Read/Write                                                                                                                        |

| 1   | Erase                    | Set to erase storage scope display. Sets READY bit 7 at end of erase.                                                                                                                                       |

| 0   | Intensification          | Set to delay display until scope deflects to new X, Y values, then strobes intensification (Z axis) and sets READY bit 7.                                                                                   |

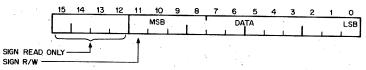

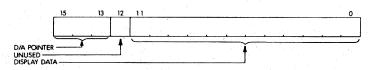

## Data Registers (DAC) 776 760 to 776 766

DAC1 and 2 may be used either in conjunction with the scope or for D/A channels. DAC3 and 4 may be used for additional D/A channels.

|       | the state of the s |                             |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| BIT   | NAME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | FUNCTION                    |

| 15-12 | Sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Read only (2's complement)  |

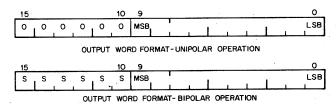

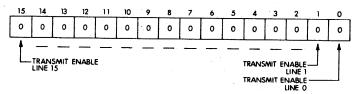

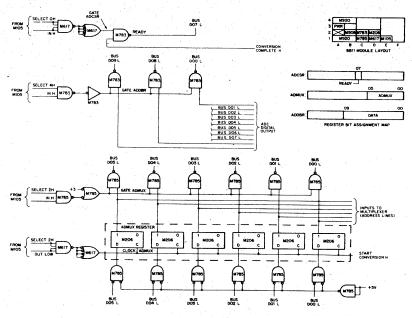

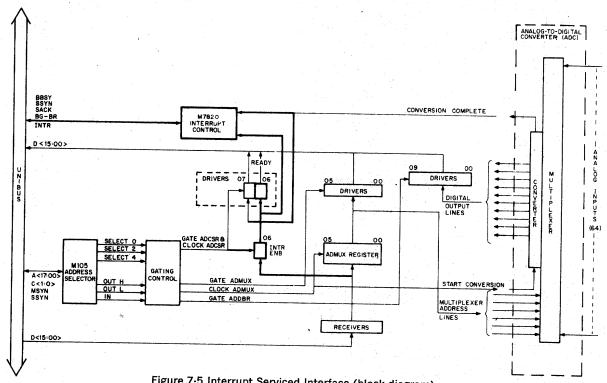

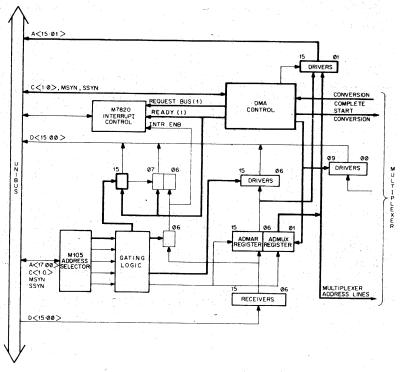

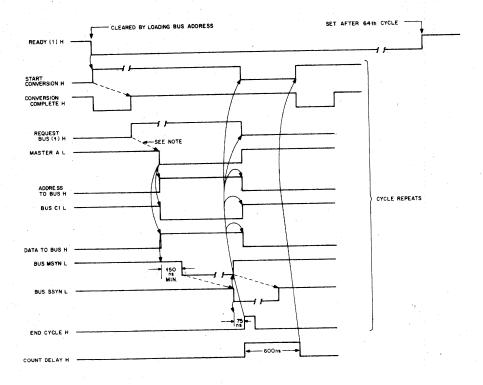

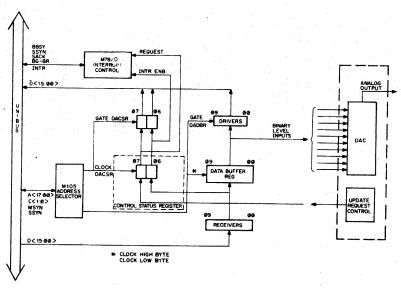

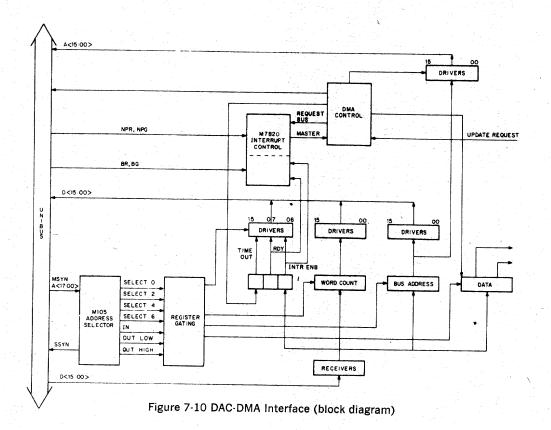

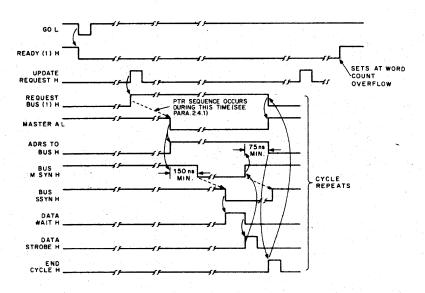

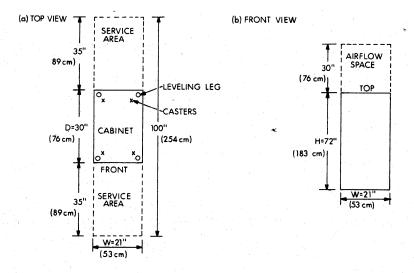

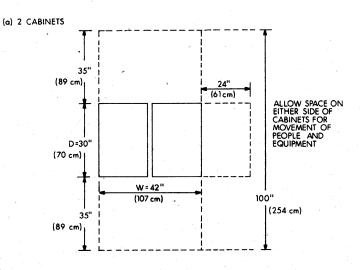

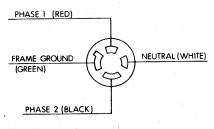

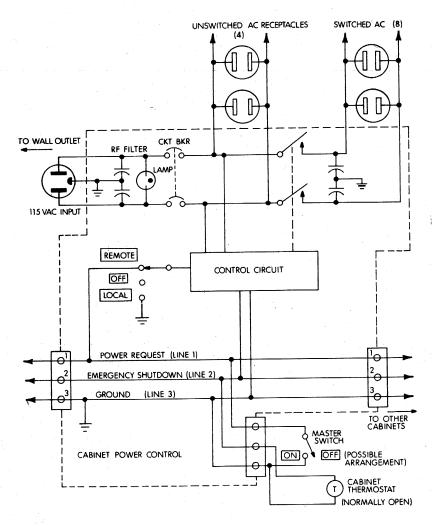

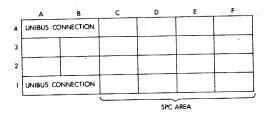

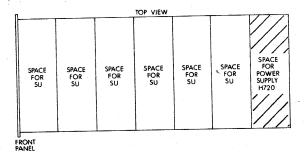

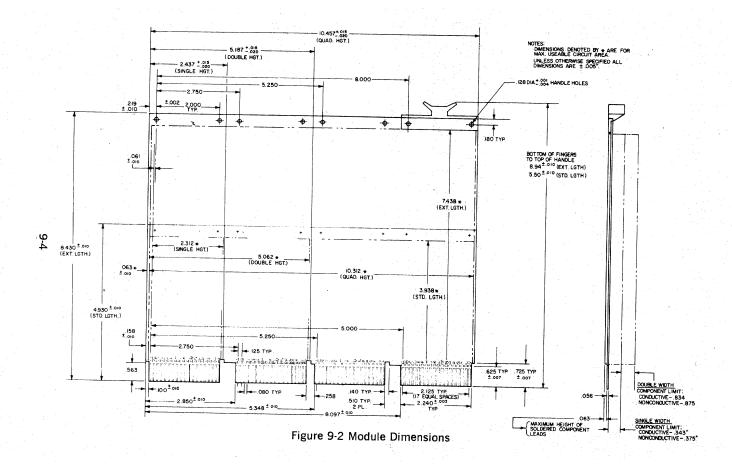

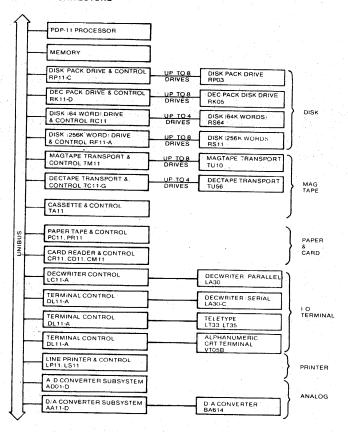

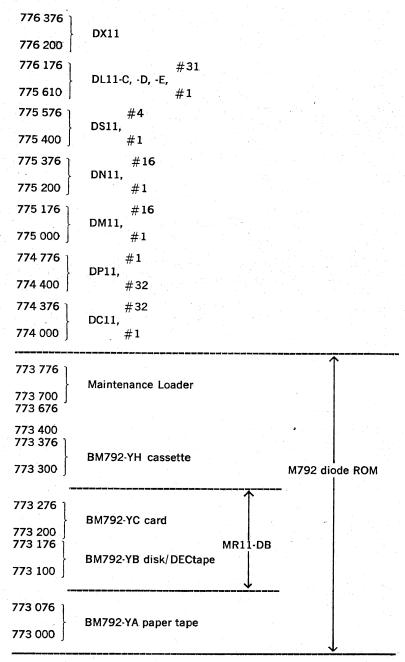

| 11    | Sign                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Read/Write (2's complement) |